TMS320C6657CZHA IC DSP PUNTO FIXO/FLOTANTE 625FCBGA

Parámetro do produto

Descrición

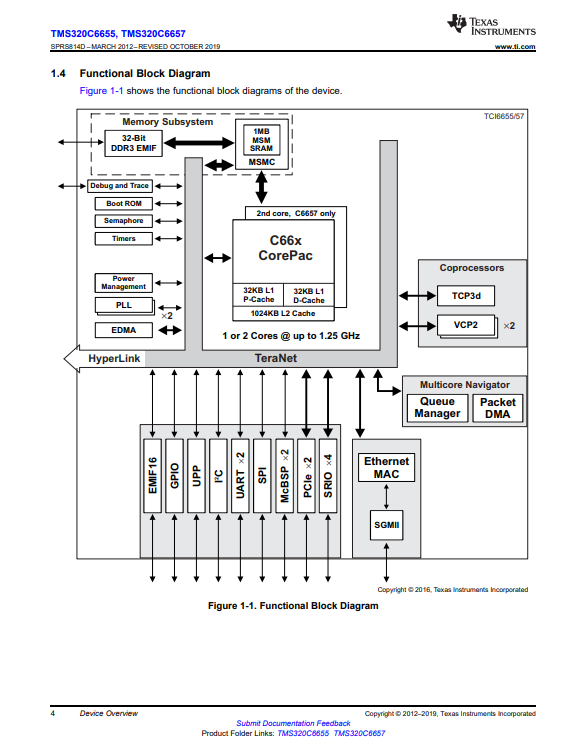

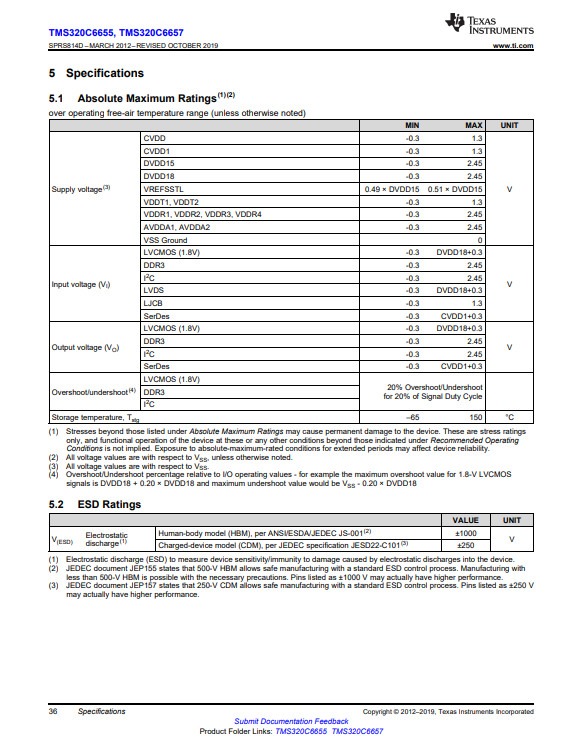

A arquitectura KeyStone de TI ofrece unha plataforma programable que integra varios subsistemas (núcleos C66x, subsistema de memoria, periféricos e aceleradores) e utiliza varios compoñentes e técnicas innovadoras para maximizar a comunicación intradispositivo e entre dispositivos que permite que os distintos recursos DSP funcionen de forma eficiente e sen problemas.O elemento central desta arquitectura son compoñentes clave como Multicore Navigator que permite unha xestión eficiente de datos entre os distintos compoñentes do dispositivo.TeraNet é un tecido de conmutadores sen bloqueo que permite un movemento de datos internos rápido e sen conflitos.O controlador de memoria compartida multinúcleo permite o acceso á memoria compartida e externa directamente sen aproveitar a capacidade do switch.Para o uso de punto fixo, o núcleo C66x ten 4 veces a capacidade de acumulación de multiplicación (MAC) dos núcleos C64x+.Ademais, o núcleo C66x integra capacidade de punto flotante e o rendemento computacional bruto por núcleo é un líder na industria de 40 GMACS por núcleo e 20 GFLOPS por núcleo (@frecuencia de operación de 1,25 GHz).O núcleo C66x pode executar 8 operacións MAC de punto flotante de precisión única por ciclo e pode realizar operacións de precisión dobre e mixta e cumpre IEEE 754.O núcleo C66x incorpora 90 novas instrucións (en comparación co núcleo C64x+) dirixidas ao procesamento orientado a matemáticas vector e coma flotante.Estas melloras producen melloras considerables no rendemento nos núcleos DSP populares utilizados en funcións de procesamento de sinal, matemáticas e adquisición de imaxes.O núcleo C66x é compatible con códigos anteriores cos núcleos DSP de punto fixo e flotante C6000 da xeración anterior de TI, o que garante a portabilidade do software e ciclos de desenvolvemento de software reducidos para as aplicacións que migran a hardware máis rápido.O DSP C665x integra unha gran cantidade de memoria no chip.Ademais dos 32 KB de caché de datos e programas L1, pódense configurar 1024 KB de memoria dedicada como memoria RAM ou caché asignada.O dispositivo tamén integra 1024 KB de memoria compartida multinúcleo que se pode usar como SRAM L2 compartida e/ou SRAM L3 compartida.Todas as memorias L2 incorporan detección e corrección de erros.Para un acceso rápido á memoria externa, este dispositivo inclúe unha interface de memoria externa (EMIF) DDR-3 de 32 bits que funciona a unha velocidade de 1333 MHz e admite ECC DRAM.

| Especificacións: | |

| Atributo | Valor |

| Categoría | Circuítos integrados (CI) |

| Integrado - DSP (procesadores de sinal dixital) | |

| Mfr | Texas Instruments |

| Serie | TMS320C66x |

| Paquete | Bandexa |

| Estado da peza | Activo |

| Tipo | Punto fixo/flotante |

| Interface | DDR3, EBI/EMI, Ethernet, McBSP, PCIe, I²C, SPI, UART, UPP |

| Velocidade do reloxo | 1 GHz |

| Memoria non volátil | ROM (128 kB) |

| RAM no chip | 2,06 MB |

| Tensión - E/S | 1,0 V, 1,5 V, 1,8 V |

| Tensión - Núcleo | 1,00 V |

| Temperatura de operación | -40 °C ~ 100 °C (TC) |

| Tipo de montaxe | Montaxe en superficie |

| Paquete / Estuche | 625-BFBGA, FCBGA |

| Paquete de dispositivos do provedor | 625-FCBGA (21 x 21) |

| Número de produto base | TMS320 |

RelacionadoPRODUTOS

-

Tel

-

Correo electrónico

-

skype

-

whatsapp

whatsapp